# Circuits logiques et électronique numérique

- Support de cours -

COURS ING3 Année 2007-2008

Benoît Decoux

# Sommaire

| Introduction générale                                                             | 4    |

|-----------------------------------------------------------------------------------|------|

| Partie I) Fonctions logiques de base et circuits associés                         | 6    |

| I.1) Algèbre de Boole                                                             |      |

| I.1.1) Fonctions logiques de base et opérateurs correspondant                     |      |

| a) Fonctions élémentaires simples : NON, OU, ET                                   |      |

| b) Fonctions élémentaires composées : NON-ET, NON-OU, OU-EXCLUSIF, NON-OU-EXCLUSI | F.9  |

| I.1.2) Propriétés et théorèmes                                                    | 12   |

| I.2) Représentation des fonctions logiques                                        | 16   |

| I.2.1) Représentation par table de vérité                                         |      |

| I.2.2) Représentation algébrique                                                  |      |

| a) Ecriture sous forme d'une somme de produits (SDP)                              |      |

| b) Ecriture sous forme d'un produit de somme (PDS)                                |      |

| I.2.3) Expression numérique                                                       | 20   |

| I.3) Simplification des fonctions logiques                                        | 2.1  |

| I.3.1) Méthode algébrique                                                         |      |

| I.3.2) Tableaux de Karnaugh                                                       |      |

| · · · · · · · · · · · · · · · · · · ·                                             |      |

| I.4) Circuits logiques                                                            | 25   |

| Partie II) Logique combinatoire                                                   | 28   |

| II.1) Codeur/décodeur binaire                                                     | 28   |

| ÍÍ.1.1) Codeur                                                                    | 28   |

| II.1.2) Décodeur                                                                  | 29   |

| II.2) Transcodeurs                                                                | 31   |

| II.2.1) Transcodeur DCB-7 segments                                                |      |

| II.2.2) Autres transcodeurs                                                       |      |

| II.3) Multiplexeur/démultiplexeur                                                 |      |

| II.3.1) Multiplexeur                                                              |      |

| II.3.2) Démultiplexeurs                                                           |      |

| , · · · ·                                                                         |      |

| II.4) Comparateur                                                                 |      |

| II.4.1) Comparateur d'égalité                                                     |      |

| II.4.2) Comparateur complet                                                       | 38   |

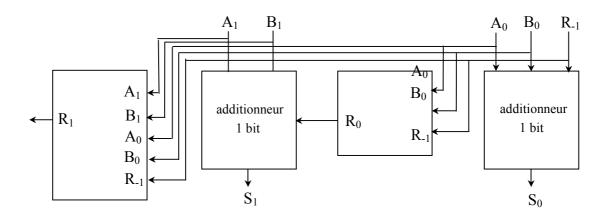

| II.5) Les Additionneurs                                                           | 40   |

| II.5.1) Demi additionneur                                                         |      |

| II.5.2) Additionneur complet                                                      |      |

| II.5.3) Additionneur de deux mots à propagation de retenue                        |      |

| II.5.4) Additionneur à anticipation de retenue                                    | 42   |

| Partie III) Logique séquentielle                                                  | . 44 |

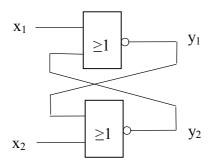

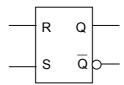

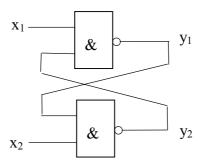

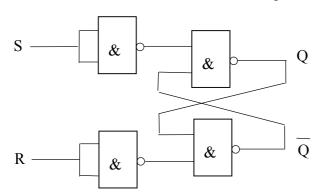

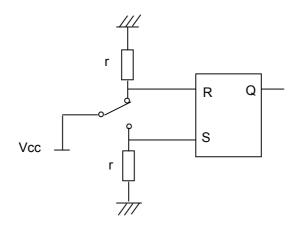

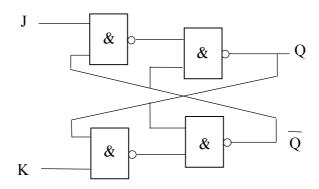

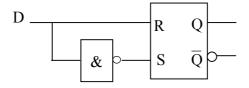

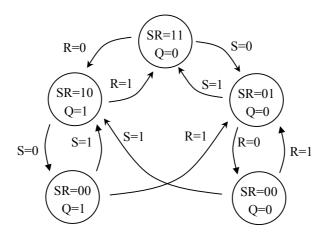

| III.1) Bascules                                                                   | 44   |

| III.1.1) Bascules asynchrones                                                     |      |

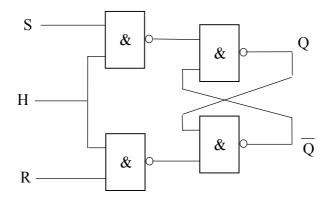

| a) Bascule RS                                                                     |      |

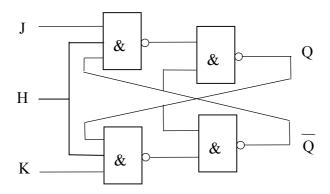

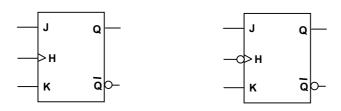

| b) Bascule JK                                                                     | 48   |

| c) Bascule D                                                                      | 49   |

| d) Bascule T                                                                      |      |

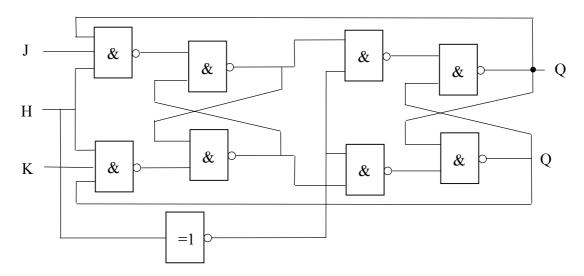

| III.1.2) Bascules synchrones                                                      |      |

| a) Synchronisation sur niveau                                                     |      |

| b) Synchronisation sur front                                                      |      |

| c) Entrées de forçage                                                             |      |

| d) Tables de transition                                                           |      |

| e) Exigences de synchronisation                                                   | 39   |

| III.2) Registres                                                       | 59  |

|------------------------------------------------------------------------|-----|

| III.2.1) Différents types de registres                                 | 59  |

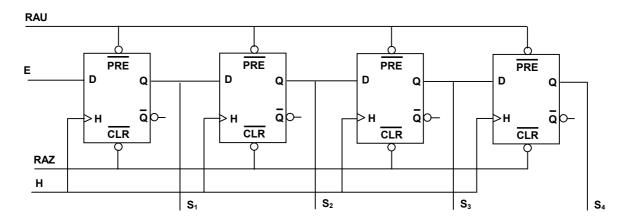

| a) Registres à entrées parallèles, sorties parallèles                  | 59  |

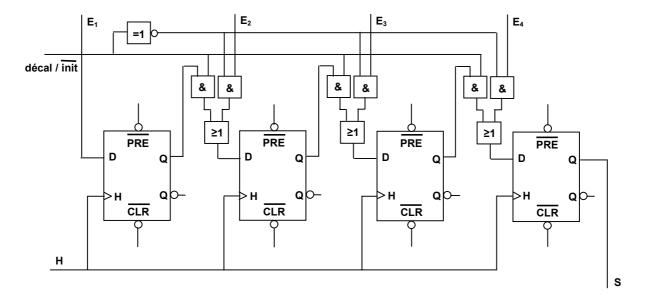

| b) Registres à entrée série, sortie série                              |     |

| c) Registres à entrée série, sorties parallèles                        |     |

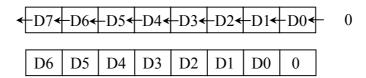

| d) Registres à entrées parallèles, sortie série                        |     |

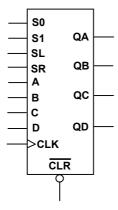

| III.2.2) Registres universels                                          |     |

| III.2.3) Application des registres                                     |     |

| a) Décalage                                                            |     |

| b) Rotation                                                            | 63  |

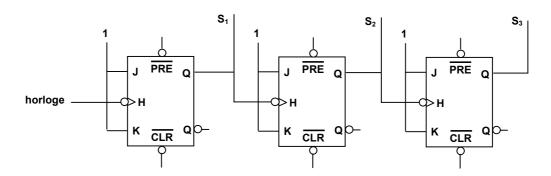

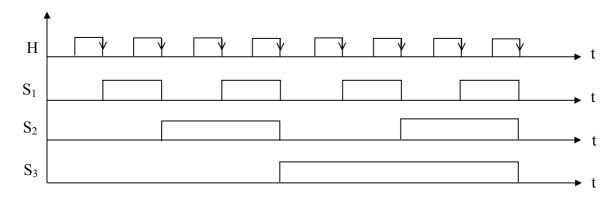

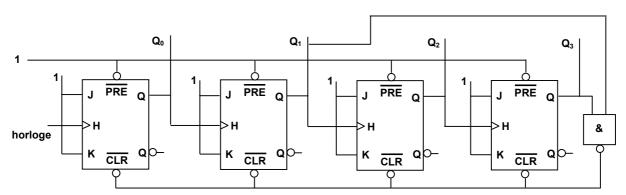

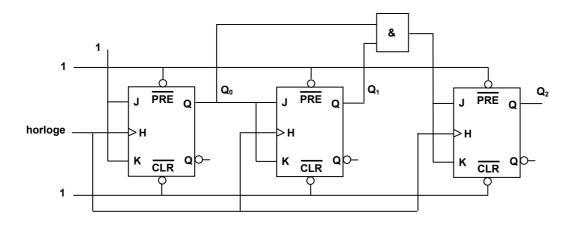

| III.3) Compteurs                                                       | 63  |

| III.3.1) Compteurs asynchrones                                         |     |

| a) Compteur binaire                                                    | 65  |

| b) Compteur modulo N                                                   |     |

| c) Inconvénients et avantages des compteurs asynchrones                | 66  |

| III.3.2) Compteurs synchrones                                          | 66  |

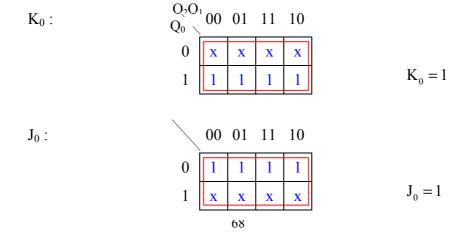

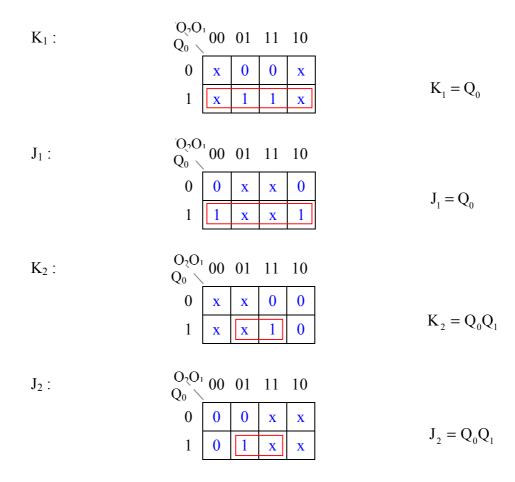

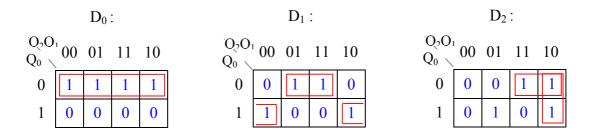

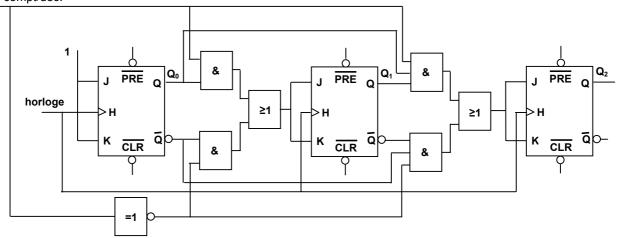

| a) Détermination directe des entrées des bascules                      | 67  |

| b) Utilisation des tables de transition                                | 68  |

| c) Compteurs/décompteurs                                               |     |

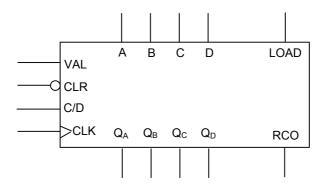

| d) Compteurs intégrés                                                  |     |

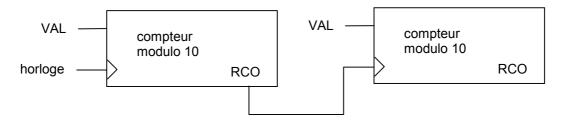

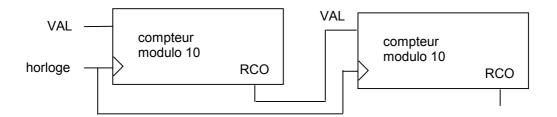

| e) Mise en cascade de compteurs                                        |     |

| III.3.3) Synchrone vs asynchrone                                       | 72  |

| III.4) Machines d'état                                                 |     |

| III.4.1) Définitions                                                   |     |

| a) Machine d'état synchrone                                            |     |

| b) Machine d'état asynchrone                                           |     |

| III.4.2) Graphes des états ou graphe des transitions                   |     |

| Dautia IV) Tankunlaria dan siyayita intérnés                           | 7.0 |

| Partie IV) Technologie des circuits intégrés                           |     |

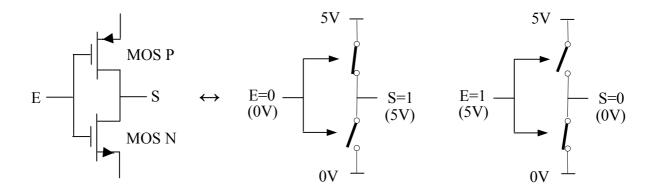

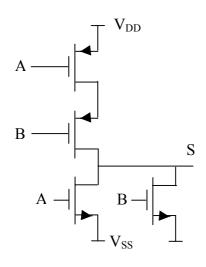

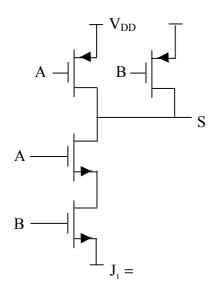

| IV.1) Description des familles TTL et CMOS                             |     |

| IV.1.1) Technologie utilisée                                           |     |

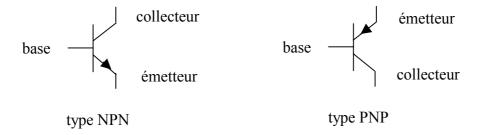

| a) Transistors bipolaires                                              |     |

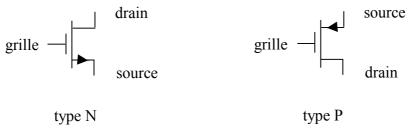

| b) Transistors MOS                                                     |     |

| c) Modèles électriques                                                 |     |

| d) Réalisation de fonctions logiques élémentaires                      |     |

| IV.1.2) Sous-familles                                                  |     |

| a) Famille TTL                                                         |     |

| b) Famille CMOS                                                        | 79  |

| IV.2) Caractéristiques des familles TTL et CMOS                        | 80  |

| IV.2.1) Alimentation                                                   |     |

| IV.2.2) Niveaux de tension de courant                                  | 80  |

| a) Niveaux de tension d'entrée                                         | 80  |

| b) Niveaux de tension de sortie                                        |     |

| IV.2.3) Consommation                                                   |     |

| a) Consommation statique                                               |     |

| b) Consommation dynamique                                              |     |

| IV.2.4) Sortance                                                       |     |

| IV.2.5) Temps de propagation                                           |     |

| IV.2.6) Immunité aux bruits                                            |     |

| IV.2.7) Entrées non-utilisées                                          | 84  |

| IV.3) Association de portes des familles TTL et CMOS                   | 84  |

| IV.3.1) TTL vers CMOS                                                  |     |

| IV.3.2) CMOS vers TTL                                                  | 85  |

| IV.4) Avantages et inconvénients des circuits des familles TTL et CMOS | 95  |

|                                                                        |     |

# Introduction générale

Bienvenue dans le monde merveilleux de la logique et de l'électronique numérique, dans lequel on a :

$$1+1=1$$

mais aussi:

1+1=10

. . .

Dans le domaine de la logique, on distingue en général 2 grandes catégories :

- la logique combinatoire,

- la logique séquentielle.

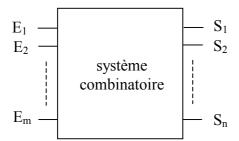

Dans les circuits combinatoires, les sorties sont déterminées uniquement en fonction des variables d'entrée. Le temps n'intervient pas dans les fonctions logiques.

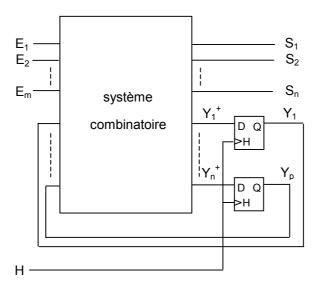

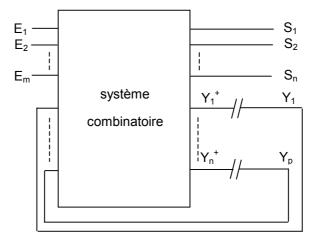

Système séquentiel à m entrées  $(E_1, E_2, ..., E_m)$ , n sorties  $(S_1, S_2, ..., S_n)$

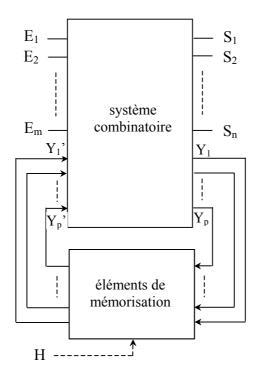

Dans un système séquentiel, l'état de sortie ne dépend pas uniquement de la combinaison des entrées à un instant donné, mais aussi de valeurs passées d'entrées, de sorties ou de variables internes. Dans notre cas, il s'agira de valeurs précédentes des sorties. En plus de dépendre des entrées présentes, les sorties présentes seront exprimées en fonction de leur valeur précédente, disponible grâce à la présence d'éléments de mémorisation. Les systèmes séquentiels sont donc des systèmes bouclés. Le schéma suivant illustre ces propriétés :

Système séquentiel à m entrées  $(E_1, E_2, ..., E_m)$ , n sorties  $(S_1, S_2, ..., S_n)$  et p variables internes  $(Y_1, Y_2, ..., Y_p)$

Sur ce schéma,  $Y_1$ ,  $Y_2$ , ...,  $Y_p$  représentent les valeurs présentes de variables internes et  $Y_1$ ,  $Y_2$ , ...,  $Y_p$  leur valeur passées. La notion de présent et de passé dépend du type de système séquentiel utilisé : il existe les système séquentiels sychrones et les systèmes séquentiels asynchrones.

Dans les systèmes séquentiels **synchrones**, c'est un signal d'horloge (une alternance, dans le temps, de 0 et de 1) qui définit le passage du passé au présent : la mise à jour des variables présentes  $Y_1$ ,  $Y_2$ , ..., $Y_p$  se produit à chaque "coup" d'horloge. Ce signal est représenté en pointillé sur le schéma ci-dessus.

Dans les systèmes séquentiels **asynchrones**, les éléments de mémorisation sont constitués par un retour direct. La mise à jour des variables présentes  $Y_1$ ,  $Y_2$ , ...,  $Y_p$  est donc quasi-instantanée après la mise à jour des variables passées  $Y_1$ ,  $Y_2$ , ...,  $Y_p$ .

Par exemple, un compteur est un système séquentiel qui ne possède comme entrée qu'un signal d'horloge. A chaque coup d'horloge, sa valeur de sortie binaire s'incrémente. A un instant donné, sa sortie dépend de sa valeur au coup d'horloge précédent.

#### Plan du cours

Le cours sera subdivisé en 4 grandes parties :

- 1) Fonctions logiques de base et circuits associés :

- Fonctions simples : NON, ET et OU, et fonctions composées : fonctions NON-ET, NON-OU, OU EXCLUSIF, et opérateurs logiques correspondant.

- Algèbre de Boole

- 2) Logique combinatoire :

- Codeur/décodeur, transcodeur, multiplexeur, additionneur...

- 3) Logique séquentielle :

- Bascules, registres, compteurs...

- 4) Familles de circuits intégrés logiques :

- Etude des différences entre les familles TTL et CMOS.

#### Du point de vue électronique...

Concrètement, lors de la réalisation de circuits électroniques numériques, les 2 niveaux logiques sont constitués par 2 tensions différentes. La tension correspondant au niveau 0 est en général 0V. La tension correspondant au niveau 1 dépend de la technologie utilisée. Une norme couramment répandue est la norme TTL :

```

niveau logique 0 \leftrightarrow 0 Volts niveau logique 1 \leftrightarrow 5 Volts

```

Les opérateurs logiques de base et d'autres fonctions logiques plus évoluées existent sous forme de circuits intégrés.

#### *Vocabulaire*

Dans ce cours, un vocabulaire spécifique au domaine de la logique sera utilisé.

Le **bit** est l'élément de base de la logique binaire : il vaut 0 ou 1. C'est l'équivalent du chiffre dans le domaine décimal (0 à 9).

Un **mot** binaire est composé d'un nombre variables de bits. On peut également parler de **nombre binaire**.

En général, la logique utilisée est la **logique positive**, dans laquelle le niveau dit actif est le niveau 1. Ca sera le cas dans la totalité de ce cours. Mais il existe également la logique négative, dans laquelle il s'agit du 0.

# Partie I) Fonctions logiques de base et circuits associés

Cette partie abordera la représentation des fonctions sous forme algébrique, sous forme de table de vérité puis sous forme de shémas, et leur simplification au moyen des règles de l'algèbre de Boole et des tableaux de Karnaugh.

# I.1) Algèbre de Boole

Georges Boole, philosophe et mathématicien irlandais du 19<sup>ème</sup> siècle est l'auteur d'une théorie sur l'art de construire un raisonnement logique au moyen de propositions qui ont une seule réponse OUI (VRAI) ou NON (FAUX). L'ensemble des opérations formelles appliquées à ces propositions forme une structure mathématique appelée algèbre de Boole. A son époque, il s'agissait de développement purement théorique car on ignorait l'importance qu'allait prendre cette algèbre avec l'informatique.

Les concepts de la logique booléenne ont été ensuite appliqués aux circuits électroniques par Claude Shannon (1916-2001).

Cette algèbre est applicable à l'étude des systèmes possédant deux états s'excluant mutuellement. Dans la logique positive (la plus couramment utilisée), on associe OUI à 1 et NON à 0. Dans la logique négative, c'est l'inverse.

L'algèbre booléenne binaire est à la base de la mise en œuvre de tous les systèmes numériques : ordinateurs, systèmes numériques portables, systèmes de communication numériques, etc. Elle permet entre autres de simplifier les fonctions logiques, et donc les circuits électroniques associés.

#### I.1.1) Fonctions logiques de base et opérateurs correspondant

Une fonction logique est une fonction d'une ou plusieurs variables logiques, combinées entre elles par 3 fonctions élémentaires simples : NON, OU et ET.

Il existe également des fonctions élémentaires composées de fonctions élémentaires simples : NON-ET, NON-OU, OU-EXCLUSIF, NON-OU-EXCLUSIF.

Elles peuvent être représentées schématiquement pas des opérateurs logiques, encore appelés portes logiques.

# a) Fonctions élémentaires simples : NON, OU, ET

#### **Fonction NON (ou fonction complément)**

Soit A une variable quelconque. La fonction complément de la variable A est notée :

$$F(A) = \overline{A}$$

(prononcer "a barre", "non A", ou encore "complément de A").

Remarque : une variable est également appelée "littéral".

Cette fonction affecte à la variable de sortie l'état complémentaire de la variable d'entrée.

#### Table de vérité

On peut exprimer cette propriété sous forme d'un tableau entrée/sortie, appelé table de vérité :

| A | F(A) |

|---|------|

| 0 | 1    |

| 1 | 0    |

Le nom anglais de la fonction complément est "NOT".

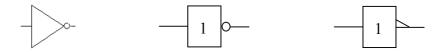

## Symboles

Il existe deux types de symbole pour représenter cet opérateur. Le symbole américain, très utilisé dans les logiciels de simulation (à gauche sur la figure ci-dessous), et les symboles européens, normalisés (au milieu et à droite).

Le cercle est en général utilisé pour indiquer une complémentation. On appelle souvent cet opérateur "inverseur".

# Fonction OU (ou somme logique)

La fonction logique OU est également appelée "somme logique", ou "union logique". Sa notation algébrique utilise le symbole de la somme arithmétique. Pour 2 variables A et B, on a :

$$F(A, B) = A+B$$

Le terme anglais est "OR".

#### Table de vérité

| A | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

## Symboles

# Remarque 1

On verra plus loin que la somme logique est différente de la somme arithmétique. Dans le cas de la fonction OU, on a :

$$1+1=1$$

Avec l'opération arithmétique +, on aurait :

$$1+1=10$$

(en d'autres termes, le résultat est 0 avec une retenue égale à 1).

# Remarque 2

On pourrait avoir plus de 2 variables. Par exemple, pour 3 variables :

| A | В | С | A+B+C |

|---|---|---|-------|

| 0 | 0 | 0 | 0     |

| 0 | 0 | 1 | 1     |

| 0 | 1 | 0 | 1     |

| 0 | 1 | 1 | 1     |

| 1 | 0 | 0 | 1     |

| 1 | 0 | 1 | 1     |

| 1 | 1 | 0 | 1     |

| 1 | 1 | 1 | 1     |

Le symbole correspondant serait le même mais avec 3 entrées.

# **Fonction ET (ou produit logique)**

La fonction ET est également appelée "produit logique", ou "intersection logique". Sa notation algébrique utilise le symbole de la multiplication arithmétique :

$$F(A, B) = A \times B$$

ou encore:

$$F(A, B) = A.B$$

ou plus simplement

$$F(A, B) = AB$$

Le terme anglais est "AND".

Table de vérité

| Α | В | $A \times B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 0            |

| 1 | 0 | 0            |

| 1 | 1 | 1            |

# **Symboles**

#### Remarque

Avec la fonction ET à plus de 2 entrées, le seul cas où la sortie serait à 1 serait le cas où toutes les entrées sont à 1

#### Illustration

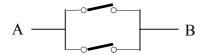

Pour se souvenir des fonctions OU et ET, on peut utiliser une analogie électrique : des interrupteurs fermés ou ouverts et donc laissant passer le courant ou non :

- interrupteurs en parallèle pour le OU;

- interrupteurs en série pour le ET.

La correspondance entre l'état de l'interrupteur et le niveau logique est :

ouvert (le courant ne passe pas) ↔ niveau logique 0 fermé (le courant passe) ↔ niveau logique 1

Le courant passe de A à B si l'un OU l'autre des 2 interrupteurs est fermé.

Le courant passe de A à B si l'un ET l'autre des 2 interrupteurs sont fermés.

# Exemple de fonction composée de ces 3 fonctions de base

Soit la fonction logique suivante, de 4 variables A, B, C et D:

$$f(A, B, C, D) = A.B.C.D + A.B.C.D + A.B.C.D$$

On souhaiterait savoir pour quelles valeurs des variables cette fonction vaut 1.

La fonction étant une somme logique, elle vaut 1 si au moins un des termes de la somme vaut 1. Chaque terme étant un produit logique, il vaut 1 si tous ses termes valent 1, soit si :

$$A = B = C = D = 1$$

$A = 1; B = 0; C = 0; D = 1$

$A = 0; B = 0; C = 0; D = 0$

Donc, sur les 16 combinaisons possibles des variables d'entrée A, B, C, D, 3 seulement provoquent un 1 en sortie.

# b) Fonctions élémentaires composées : NON-ET, NON-OU, OU-EXCLUSIF, NON-OU-EXCLUSIF

Les fonctions élémentaires composées (ou combinées, ou induits) sont obtenues en combinant entre eux les fonctions élémentaires simples NON, ET et OU. L'ensemble des fonctions élémentaires simples et des fonctions élémentaires combinées NON-ET, NON-OU, OU-EXCLUSIF, NON-OU-EXCLUSIF définissent un ensemble complet d'opérateurs.

# Fonction NON-OU (NOR)

La fonction NON-OU est obtenue en complémentant la sortie d'un OU, c'est à dire en appliquant la sortie de la fonction OU à la fonction NON. Pour 2 variables A et B, elle est notée :

$$F(A, B) = \overline{A + B}$$

On utilise également la notation (moins courante) :

$$F(A, B) = A \downarrow B$$

Table de vérité

Pour obtenir ta table de vérité du non-OU, il suffit d'inverser les valeurs de sortie dans la table de vérité du OU :

| A | В | $\overline{A+B}$ |

|---|---|------------------|

| 0 | 0 | 1                |

| 0 | 1 | 0                |

| 1 | 0 | 0                |

| 1 | 1 | 0                |

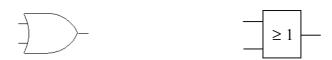

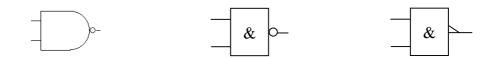

**Symboles**

# **Fonction NON-ET (NAND)**

La fonction NON-ET est obtenue en complémentant la sortie d'un ET, c'est à dire en appliquant la sortie de la fonction ET à la fonction NON. Pour 2 variables A et B, elle est notée :

$$F(A, B) = \overline{A.B}$$

On utilise également la notation :

$$F(A, B) = A \uparrow B$$

Table de vérité

Pour obtenir la table de vérité du non-ET, il suffit d'inverser les valeurs de sortie dans la table de vérité du ET :

| A | В | $\overline{A.B}$ |

|---|---|------------------|

| 0 | 0 | 1                |

| 0 | 1 | 1                |

| 1 | 0 | 1                |

| 1 | 1 | 0                |

# **Symboles**

# Fonction OU EXCLUSIF (XOR)

Pour 2 variables A et B, la fonction OU EXCLUSIF est définie par :

$$F(A, B) = A.\overline{B} + \overline{A}.B$$

On la note également :

$$F(A, B) = A \oplus B$$

Table de vérité

Pour 2 variables, le OU EXCLUSIF vaut 1 si une et une seule des deux variables d'entrée est à 1.

| Α | В | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

Avec 2 variables, on peut considérer le OU-EXCLUSIF comme un détecteur d'inégalité, puisque sa sortie est à 1 quand ses 2 entrées sont différentes.

Pour un nombre supérieur de variables, la fonction OU-EXCLUSIF vaut 1 quand les variables d'entrée à 1 sont en nombre pair. Il s'agit donc également d'un détecteur de parité.

Symboles utilisés

#### Fonction NON-OU EXCLUSIF (XNOR)

La fonction NON-OU EXCLUSIF est obtenue en complémentant la sortie d'un OU EXCLUSIF, c'est à dire en appliquant la sortie de la fonction OU EXCLUSIF à la fonction NON. Pour 2 variables A et B, elle est notée :

$$F(A, B) = \overline{A \oplus B}$$

On peut montrer qu'elle est égale à :

$$\overline{A \oplus B} = A.B + \overline{A.B}$$

11

Démonstration (utilise des propriétés étudiées dans le paragraphe suivant) :

$$\overline{A \oplus B} = \overline{A \overline{B} + \overline{A} B} = \overline{A \overline{B} \overline{A} B} = (\overline{A} + \overline{B}).(\overline{A} + \overline{B})$$

$$= (\overline{A} + B).(A + \overline{B}) = \overline{A}.A + \overline{A}B + B.A + B.\overline{B}$$

$$= A.B + \overline{A}B$$

Table de vérité

Pour obtenir la table de vérité du NON-OU EXCLUSIF, il suffit d'inverser les valeurs de sortie dans la table de vérité du OU EXCLUSIF :

| A | В | F(A,B) |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

Symbole

# I.1.2) Propriétés et théorèmes

# a) Fonctions élémentaires simples NON, OU, ET

Commutativité

$$A+B=B+A$$

$$A.B=B.A$$

Associativité

Eléments neutres

$$A+0=A$$

$$A.1=A$$

Eléments absorbants

Idempotence (ou redondance)

Propriétés de la fonction complément

Théorème de DeMorgan

Le complément d'une somme est égal au produit des termes complémentés :

$$\overline{A + B} = \overline{AB}$$

Le complément d'un produit est égal à la somme des termes complémentés :

$$\overline{A.B} = \overline{A} + \overline{B}$$

Cette propriété est généralisable à n variables.

Double distributivité

Distributivité du produit par rapport à la somme :

$$A.(B+C)=AB+AC$$

Distributivité de la somme par rapport au produit :

$$A+(B.C)=(A+B).(A+C)$$

De la droite vers la gauche du signe égal, on parle de factorisation.

La 2<sup>e</sup> propriété peut sembler étonnante : c'est la seule propriété de ce paragraphe qui diffère de celles de l'algèbre traditionnelle. On pourra pourtant vérifier qu'elle est exacte, en utilisant les propriétés d'idempotence et d'élément neutre :

Absorption

Lorsqu'une somme logique contient un terme et un de ses multiples, on peut négliger le multiple :

$$A+A.B=A$$

On peut constater que cette règle reste vraie si on intervertit les opération ET et OU :

$$A.(A+B) = A$$

Absorption du complément

1) Absorption du complément dans une somme :

$$A + \overline{A}B = A + B$$

Démonstration:

$$A + B = (A + \overline{A})(A + B)$$

$$= AA + \overline{A}A + AB + \overline{A}B$$

$$= A + \overline{A}A + AB + \overline{A}B$$

$$= A + AB + \overline{A}B$$

$$= A + AB + \overline{A}B$$

$$= A.(1 + B) + \overline{A}B$$

$$= A + \overline{A}B$$

De la même manière :

$$\overline{A} + A.B = \overline{A} + B$$

2) Absorption du complément dans un produit :

$$A.(\overline{A} + B) = A.B$$

Démonstration:

$$A.(\overline{A} + B) = A\overline{A} + AB$$

$$= AB$$

Principe de dualité

Le principe de dualité énonce que :

"Toute expression logique vraie demeure vraie si on remplace les + par des . , les 0 par des 1 et les 1 par des 0"

Exemples:

$$A+1=1 \leftrightarrow A.0=0$$

$A+\overline{A}B=A+B \leftrightarrow A(\overline{A}+B)=AB$

$A+B=1$ : vrai si A=1 ou B=1  $\leftrightarrow A.B=0$ : vrai si A=0 ou B=0

Théorème des consensus

$$\boxed{A.B + \overline{A}.C + B.C = A.B + \overline{A}.C}$$

$$(A + B).(\overline{A} + C).(B + C) = (A + B).(\overline{A} + C)$$

Le 2<sup>e</sup> est le dual du 1<sup>er</sup> ; on peut donc l'obtenir par application du principe de dualité.

# b) Fonctions élémentaires composées NON-OU, NON-ET, OU EXCLUSIF, NON-OU EXCLUSIF

Commutativité

Le NON-OU et le NON-ET, le OU EXCLUSIF et le NON-OU EXCLUSIF sont commutatifs.

#### Associativité

Le NON-OU et le NON-ET ne sont pas associatifs :

$$\frac{\overline{A.B.C}}{\overline{A+B}+C} \neq \overline{A.\overline{B.C}}$$

Le OU EXCLUSIF et le NON-OU EXCLUSIF sont associatifs.

Vérification de l'associativité du OU EXCLUSIF en étudiant le cas de 3 variables. En calculant d'abord  $A\oplus B\,$  :

| A | В | $A \oplus B$ | С | $A \oplus B \oplus C$ |

|---|---|--------------|---|-----------------------|

| 0 | 0 | 0            | 0 | 0                     |

| 0 | 0 | 0            | 1 | 1                     |

| 0 | 1 | 1            | 0 | 1                     |

| 0 | 1 | 1            | 1 | 0                     |

| 1 | 0 | 1            | 0 | 1                     |

| 1 | 0 | 1            | 1 | 0                     |

| 1 | 1 | 0            | 0 | 0                     |

| 1 | 1 | 0            | 1 | 1                     |

Recommençons en calculant d'abord  $B \oplus C$ :

| A | В | С | $B \oplus C$ | $A \oplus B \oplus C$ |

|---|---|---|--------------|-----------------------|

| 0 | 0 | 0 | 0            | 0                     |

| 0 | 0 | 1 | 1            | 1                     |

| 0 | 1 | 0 | 1            | 1                     |

| 0 | 1 | 1 | 0            | 0                     |

| 1 | 0 | 0 | 0            | 1                     |

| 1 | 0 | 1 | 1            | 0                     |

| 1 | 1 | 0 | 1            | 0                     |

| 1 | 1 | 1 | 0            | 1                     |

On constate donc que le OU EXCLUSIF est associatif :

$$A \oplus B \oplus C = (A \oplus B) \oplus C = A \oplus (B \oplus C)$$

| A | В | $\overline{A \oplus B}$ | С | $\overline{\overline{A \oplus B} \oplus C}$ |

|---|---|-------------------------|---|---------------------------------------------|

| 0 | 0 | 1                       | 0 | 0                                           |

| 0 | 0 | 1                       | 1 | 1                                           |

| 0 | 1 | 0                       | 0 | 1                                           |

| 0 | 1 | 0                       | 1 | 0                                           |

| 1 | 0 | 0                       | 0 | 1                                           |

| 1 | 0 | 0                       | 1 | 0                                           |

| 1 | 1 | 1                       | 0 | 0                                           |

| 1 | 1 | 1                       | 1 | 1                                           |

| A | В | C | $\overline{B \oplus C}$ | $\overline{A \oplus \overline{B \oplus C}}$ |

|---|---|---|-------------------------|---------------------------------------------|

| 0 | 0 | 0 | 1                       | 0                                           |

| 0 | 0 | 1 | 0                       | 1                                           |

| 0 | 1 | 0 | 0                       | 1                                           |

| 0 | 1 | 1 | 1                       | 0                                           |

| 1 | 0 | 0 | 1                       | 1                                           |

| 1 | 0 | 1 | 0                       | 0                                           |

| 1 | 1 | 0 | 0                       | 0                                           |

| 1 | 1 | 1 | 1                       | 1                                           |

Le NON-OU EXCLUSIF est donc associatif.

Autres propriétés du OU-EXCLUSIF

On remarque que l'on a la propriété suivante :

$A \oplus A = 0$

L'élément neutre du OU-EXCLUSIF est 0.

# I.2) Représentation des fonctions logiques

Il existe plusieurs manières de représenter une fonction logique : par

- table de vérité,

- expression algébrique,

- schéma à portes logiques.

On peut passer facilement d'une représentation à l'autre. La connaissance de l'une des 3 est suffisante à la connaissance totale de la fonction.

#### I.2.1) Représentation par table de vérité

Une fonction F de n variables est entièrement décrite par l'énoncé de l'ensemble des combinaisons des variables d'entrées et de la valeur de la fonction correspondant à chaque combinaison. Cet énoncé prend généralement la forme d'un tableau à n+1 colonnes (n entrées + 1 sortie) et 2<sup>n</sup> lignes (sur n bits, on peut coder 2<sup>n</sup> valeurs différentes).

Chaque ligne comporte donc une combinaison des variables, qui valent 0 ou 1, et la valeur correspondante de la fonction F(A,B,C) qui vaut également 0 ou 1.

| A | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | F(0,0,0) |

| 0 | 0 | 1 | F(0,0,1) |

| 0 | 1 | 0 | F(0,1,0) |

| 0 | 1 | 1 | F(0,1,1) |

| 1 | 0 | 0 | F(1,0,0) |

| 1 | 0 | 1 | F(1,0,1) |

| 1 | 1 | 0 | F(1,1,0) |

| 1 | 1 | 1 | F(1,1,1) |

#### Remarque 1

Une table de vérité peut comporter plusieurs colonnes de sorties (par exemple, celle qui définirait le passage du code binaire naturel au code de Gray). Dans ce cas, il y a une fonction pour chaque sortie.

#### Remarque 2

Selon l'application, il peut y avoir des combinaisons d'entrée non-utilisées. Sous certaines conditions, on peut alors utiliser ces combinaisons pour simplifier la fonction (voir tableaux de Karnaugh, plus loin).

# Exemple

On définit la fonction logique f (A, B, C) = 1 si (A, B, C)<sub>2</sub> > 5. La table de vérité correspondante est :

| A | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 0        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 0        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

# I.2.2) Représentation algébrique

Il s'agit d'une représentation sous forme d'expression.

Une fonction logique Booléenne se présente comme une association d'opérations algébriques sur un ensemble de variables logiques. Elle peut s'exprimer comme une association de sommes et de produits logiques.

# a) Ecriture sous forme d'une somme de produits (SDP)

Cette forme est également appelée forme disjonctive. Par exemple, la fonction :

$$F(A,B,C) = \overline{A}.B.C + A.\overline{C} + A.\overline{B}.C$$

est sous forme conjonctive.

Pour mettre une fonction sous cette forme, on peut utiliser les règles de l'algèbre de Boole, et notamment la distributivité du produit par rapport à la somme.

Exemple

$$(A + B)(B + C + D) = AB + AC + AD + BB + BC + BD$$

=  $AB + AC + AD + B + BC + BD$

Forme SDP standard

Dans la **forme standard**, chacun des termes de la somme doit comporter toutes les variables.

On dit également que la fonction est sous forme normale ou canonique.

Sous cette forme standard, chacun des termes de la somme est appelé minterme.

Si une fonction n'est pas sous forme standard, on peut faire apparaître les variables manquantes. Par exemple, dans la fonction :

$$f(A,B,C,D) = A.\overline{B.C} + A.B.\overline{C.D}$$

,

il manque la variable D dans le 1<sup>er</sup> terme. Pour le faire apparaître, on peut le multiplier par

$$D + \overline{D}$$

car ce terme vaut 1, et le 1 est l'élément neutre pour le produit logique. On a donc :

$$A.\overline{B.C} = A.\overline{B.C.(D + \overline{D})} = A.\overline{B.C.D} + A.\overline{B.C.\overline{D}}$$

d'où la fonction:

$$f(A, B, C, D) = A.\overline{B}.C.D + A.\overline{B}.C.\overline{D} + A.B.\overline{C}.D$$

L'intérêt de la forme standard est de faciliter l'écriture de la table de vérité et des tableaux de Karnaugh (voir plus loin). Elle permet de remplir directement des derniers.

Détermination de l'expression algébrique à partir de la table de vérité

Pour chaque ligne où la sortie vaut 1, on effectue les produits des variables d'entrée, complémentées si elles valent 0, non complémentées si elles valent 1. Puis on effectue la somme de ces différents produits.

Par exemple, pour la fonction OU:

| A | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

La forme disjonctive de la fonction est :

$$F(A,B) = \overline{A}B + A\overline{B} + AB$$

Par utilisation des règles de l'algèbre de Boole, on retrouve bien l'expression de la fonction OU :

$$\overline{A}.B + A.\overline{B} + A.B = (A + \overline{A}).B + A.\overline{B} = B + A.\overline{B} = A + B$$

#### b) Ecriture sous forme d'un produit de somme (PDS)

Cette forme est également appelée forme **conjonctive**. Par exemple, la fonction :

$$F(A,B,C) = (\overline{A} + B + C).(A + \overline{C}).(A + \overline{B} + C)$$

est sous forme disjonctive.

Forme PDS standard

Dans la forme disjonctive standard, chaque terme du produit contient toutes les variables. La fonction de l'exemple ci-dessus n'est pas sous la **forme standard**.

Chacun des termes de la forme PDS standard est appelé maxterme.

Pour mettre une fonction sous forme standard, une méthode consiste à faire apparaître les variables manquantes en utilisant la propriété :

$$A\overline{A} = 0$$

où A est une variable quelconque, et la propriété de distributivité de la somme par rapport au produit (rappel : A + BC = (A + B).(A + C)).

A chaque terme du produit auquel il manque des variables, on introduit ces dernières en utilisant cette propriété. Par exemple pour la fonction suivante de 3 variables A, B et C :

$$(A+B)(\overline{A}+B+\overline{C}) = (A+B+0)(\overline{A}+B+\overline{C}) = (A+B+C\overline{C})(\overline{A}+B+\overline{C}) = (A+B+C)(\overline{A}+B+\overline{C})$$

Détermination de la forme PDS à partir de la table de vérité

Pour déterminer l'expression de la fonction sous forme disjonctive standard à partir de la table de vérité, on considère les lignes où la fonction vaut 0 ; chaque 0 de la sortie correspond à un terme du PDS.

On écrit d'abord la forme SDP comme on l'a fait précédemment ; le résultat correspond à  $\overline{F}$ . On doit alors transformer la SDP en PDS en utilisant les règles de l'algèbre de Boole.

Par exemple, pour la table de vérité du OU EXCLUSIF :

| A | В | F(A,B) |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

On a:

$$\overline{F(A,B)} = \overline{AB} + A.B = \overline{A+B} + \overline{\overline{A}+\overline{B}} = \overline{(A+B).(\overline{A}+\overline{B})}$$

d'où

$$F(A,B) = (A+B).(\overline{A}+\overline{B})$$

On peut remarquer qu'on peut également écrire directement le PDS à partir de la table, en considérant les lignes où F vaut 0, et en complémentant les variables.

# Exemple

On cherche à déterminer l'expression algébrique, d'abord sous forme SDP puis sous forme PDS, standard puis simplifiée, de la fonction définie par la table de vérité suivante :

| Α | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 1        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

Forme SDP:

$$F = \overline{AB}.C + A\overline{BC} + A\overline{B}.C + A.B.\overline{C} + A.B.C \quad \text{(forme standard)}$$

$$= \overline{AB}.C + A\overline{B}.(\overline{C} + C) + A.B.(\overline{C} + C)$$

$$= \overline{AB}.C + A.(\overline{B} + B)$$

$$= A + \overline{B}.C \quad \text{(forme simplifiée)}$$

Forme PDS:

1<sup>ère</sup> méthode:

$$\overline{F} = \overline{ABC} + \overline{A}.B.\overline{C} + \overline{A}.B.C$$

$$= \overline{A + B + C} + \overline{A + \overline{B} + C} + \overline{A + \overline{B} + \overline{C}}$$

$$= \overline{(A + B + C).(A + \overline{B} + C).(A + \overline{B} + \overline{C})}$$

(forme standard)

d'où

$$F = (A + B + C).(A + \overline{B} + C).(A + \overline{B} + \overline{C})$$

2<sup>e</sup> méthode : la détermination est directe :

$$F = (A + B + C).(A + \overline{B} + C).(A + \overline{B} + \overline{C})$$

(forme standard)

Détermination de la forme PDS à partir de la forme SDP

On peut passer de la forme disjonctive à la forme conjonctive en effectuant des factorisations, et en utilisant la propriété de distributivité de la somme par rapport au produit.

On peut également utiliser une méthode plus systématique, consistant à

- calculer  $\overline{F}$  et le mettre sous forme SDP

- lui appliquer le principe de dualité à l'expression obtenue, en :

- remplaçant F par  $\overline{F}$ ;

- remplaçant × par + et vice-versa;

- complémentant les variables.

Par exemple, avec la fonction OU EXCLUSIF sous forme PDS standard :

$$F(A,B) = \overline{A}B + A\overline{B}$$

On a:

$$\overline{F} = \overline{\overline{A}.B + A.\overline{B}} = \overline{\overline{A}.BA.\overline{B}} = (A + \overline{B})(\overline{A} + B) = A.\overline{A} + \overline{B.A} + A.B + \overline{B}.B = \overline{BA} + A.B$$

On applique alors les transformations décrites ci-dessus à cette dernière expression, et on obtient

$$F = (A + B).(\overline{A} + \overline{B})$$

#### I.2.3) Expression numérique

Pour simplifier la représentation de la fonction, on peut l'exprimer sous forme numérique. Cette forme indique la valeur décimale correspondant aux combinaisons binaires des variables, pour lesquelles la fonction vaut 1.

Par exemple, pour la fonction OU-EXCLUSIF, dont on rappelle la table de vérité :

| A | В | F(A,B) |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

Elle peut être notée :

$$f(A,B,C) = \Sigma (1,2)$$

De même, la fonction logique définie par :

$$f(A, B, C) = 1 \text{ si } (A, B, C)_2 > 5$$

peut être notée sous la forme :

$$f(A,B,C) = \Sigma (6,7)$$

## I.3) Simplification des fonctions logiques

En pratique, les fonctions logiques sont réalisées avec des circuits électroniques. Généralement, on cherche à représenter la fonction avec un minimum de termes car une fonction simplifiée utilisera moins de circuits. Elle sera exécutée plus rapidement (une porte logique possède un temps de propagation) et à un moindre coût.

Quand on parle de simplification, on sous-entend qu'une même complémentation (barre de surlignage) ne peut s'étendre sur plus d'une variable. Si ça n'est pas le cas, la fonction peut encore être simplifiée.

#### I.3.1) Méthode algébrique

On utilise les différents théorèmes et propriétés de l'algèbre de Boole.

Exemple 1

Simplification de la fonction

$$F(A,B,C)=AB+A(B+C)+B(B+C)$$

On a:

Exemple 2

$$F = [A\overline{B}(C + BD) + \overline{AB}]C$$

$$= [A\overline{B}C + A\overline{B}BD + \overline{AB}]C = [A\overline{B}C + A.0.D + \overline{AB}]C = [A\overline{B}C + 0 + \overline{AB}]C$$

$$= [A\overline{B}C + \overline{AB}]C = A\overline{B}CC + \overline{AB}C = A\overline{B}C + \overline{AB}C = (A + \overline{A}.)\overline{B}C$$

$$= \overline{B}.C$$

# I.3.2) Tableaux de Karnaugh

Les tableaux de Karnaugh constituent une autre représentation de la table de vérité de la fonction. Ils permettent de simplifier les fonctions logiques de manière graphique.

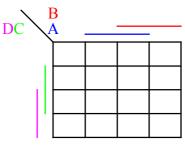

# Principe

Les variables d'entrée sont placées dans la 1<sup>ère</sup> case en haut à gauche du tableau. Elle sont réparties en lignes et colonnes. Par exemple, pour 3 variables, on peut en utiliser 2 pour constituer 4 lignes (correspondant aux 4 combinaisons de ces 2 variables) et 1 pour constituer 2 colonnes (correspondant aux 2 valeurs de cette variable).

Pour que la simplification puisse se faire, il faut qu'entre 2 lignes et 2 colonnes adjacentes, 1 seul bit change dans les combinaisons des variables. Cette règle doit être vraie également entre la dernière ligne (ou colonne) et la première. On peut pour cela utiliser le code binaire réfléchi (ou "code de Gray"), qui possède ces caractéristiques.

Par exemple, le code binaire réfléchi pour 2 bits est :

puis pour 3 bits:

Il y a bien un seul bit différent entre la dernière combinaison et la première.

Quand on ajoute une variable supplémentaire (ce qui va avoir pour effet de doubler le nombre de valeurs possibles), on la met à 0 pour les valeurs déjà définies et à 1 pour les nouvelles valeurs. Pour les autres variables, on les recopie par symétrie de leurs valeurs déjà définies (voir le passage de 2 à 3 variables ci-dessus).

Par exemple, pour la fonction suivante, issue d'une table de vérité comme vu précédemment :

$$f(A,B,C,D) = \overline{AB}.C.D + \overline{AB}.C.\overline{D} + \overline{A}.B.C.D + \overline{A}.B.C.\overline{D} + \overline{AB}.\overline{C.D} + \overline{AB}.\overline{C.D} + \overline{AB}.\overline{C.D} + \overline{AB}.\overline{C.D} + \overline{AB}.\overline{C.D}$$

| \AB<br>CD\ | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 00         | 0  | 0  | 0  | 1  |

| 01         | 0  | 0  | 0  | 1  |

| 11         | 1  | 1  | 0  | 1  |

| 10         | 1  | 1  | 0  | 1  |

Comme dans la table de vérité, chaque terme de la somme se traduit par un 1 dans le tableau. Par exemple, le 1 en haut à droite correspond au terme :

# $A.\overline{B.C.D}$

### Règles de regroupement

Une fois le tableau de Karnaugh rempli, on cherche à effectuer des regroupements. Les règles de regroupement à respecter sont :

- si on choisit de regrouper les 1, on obtient f, si on choisit les 0, on obtient  $\bar{f}$ ;

- les regroupements doivent porter sur des 1 (resp. des 0) adjacents ;

- les regroupements peuvent être uniquement carrés ou rectangulaires ;

- les regroupements peuvent porter sur 2<sup>n</sup> colonnes ou lignes, avec n entier naturel : 2, 4, 8, etc.

Dans l'exemple précédent, on peut rassembler les 1 adjacents par 2 regroupements :

| \AB<br>CD\ | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 00         | 0  | 0  | 0  | 1  |

| 01         | 0  | 0  | 0  | 1  |

| 11         | 1  | 1  | 0  | 1  |

| 10         | 1  | 1  | 0  | 1  |

Ayant dans cet exemple 2 regroupements, la fonction peut être réduite en une somme de 2 termes. Un regroupement de 2 cases sur une ligne ou une colonne élimine 1 variable ; un regroupement de 2<sup>n</sup> cases élimine n variables.

Pour le terme correspondant au regroupement de gauche, le 1 de la sortie est indépendant de la valeur de B et de D, on peut donc le simplifier en :

$$\overline{A}.C$$

De même pour le regroupement de droite :

$$A\overline{B}$$

La fonction peut donc se simplifier en :

$$f(A, B, C, D) = \overline{A}.C + A.\overline{B}$$

Si les entrées sont composées de 4 variables, on peut les séparer en 2+2 (4 lignes – 4 colonnes). Mais on aurait pu également les séparer en 3+1 (8 lignes – 2 colonnes).

#### Remarques

- La simplification peut ne pas être unique. Mais les différentes fonctions obtenues sont équivalentes, c'est à dire qu'elles possèdent même table de vérité.

- On peut trouver d'autres présentations du tableau de Karnaugh :

ou encore

|                         | Ā.B | $A\overline{B}$ | A.B | Ā.B |

|-------------------------|-----|-----------------|-----|-----|

| $\overline{\text{C.D}}$ |     |                 |     |     |

| $J_1 =$                 |     |                 |     |     |

| C.D                     |     |                 |     |     |

| C.D                     |     |                 |     |     |

Pour 1 variable :

- présence de la barre = "1"

- absence de la barre = "0"

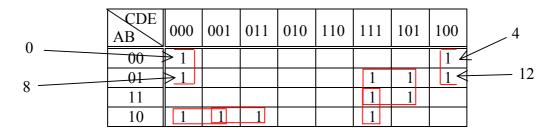

# Exemple pour cinq variables

On cherche à simplifier la fonction suivante.

$$f(A,B,C,D,E) = \Sigma(0, 4, 8, 12, 13, 15, 16, 17, 19, 23, 29, 31)$$

Il y a deux groupes de quatre 1 :  $\overline{ADE}$  correspondant aux entrées 0, 4, 8 et 12, et B.C.E à 13, 15, 31, et 29.

Il y a 3 groupes de deux 1 : A.B.C.D correspondant aux entrées 16 et 17, A.B.C.E à 19 et 23, et A.C.D.E à 23 et 31.

La fonction simplifiée est donc :

$$f(A, B, C, D, E) = \overline{ADE} + B.C.E + A\overline{BCD} + A\overline{BC}.E + ACDE$$

#### Combinaisons d'entrée non-utilisées

Il peut arriver qu'il y ait des combinaisons non-utilisées dans les variables d'entrée. Ces combinaisons correspondent à une sortie indéterminée. Par exemple, dans la table de vérité suivante :

| a | b | c | F(a,b,c) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 1        |

Tous les états possibles d'entrée ne sont pas utilisés. On met une croix dans l'emplacement correspondant du tableau de Karnaugh :

Si l'on a choisi de regrouper les 1, on remplace ces croix par des 1 de manière à permettre des regroupements plus grands. D'où la fonction simplifiée :

$$f(a, b, c) = \overline{b \cdot c} + \overline{b \cdot c} + a$$

La possibilité de simplifier ou non dépend de l'application : si l'on est sûr que les autres combinaisons d'entrée n'auront jamais lieu, on peut considérer ces états comme indifférents et donc simplifier la fonction, comme ci-dessus. Si ces combinaisons ne figurent pas dans la table de vérité mais peuvent physiquement exister, il faut préciser quand même la sortie correspondante (a priori, 0). Dans ce cas, on ne peut pas simplifier plus la fonction.

#### I.4) Circuits logiques

On a vu que chaque fonction logique élémentaire pouvait être représentée par une porte logique. C'est la représentation qui permet de passer à la réalisation pratique des fonctions logiques, c'est à dire avec des circuits intégrés.

Nous allons voir maintenant comment un circuit logique quelconque peut être réalisée à partir des opérateurs logiques élémentaires simples (NON, OU, ET) et des opérateurs logiques élémentaires composés (NON-OU, NON-ET, OU EXCLUSIF, NON-OU EXCLUSIF)..

## Utilisation de portes à 2 entrées

Il existe des circuits intégrés comportant des portes à nombre d'entrées supérieur à 2. Cependant, on utilise souvent des portes à 2 entrées (notamment pour éviter d'utiliser plusieurs circuits intégrés dans un même montage).

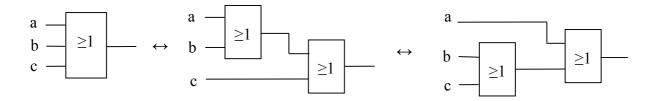

Par exemple, on a vu précédemment que le OU était associatif :

$$F=A+B+C=(A+B)+C=A+(B+C)$$

Cette propriété se traduit au niveau du circuit par les équivalences :

L'inconvénient pratique que comporte cette solution est que physiquement, une porte logique possède un temps de propagation, c'est à dire que lorsque des entrées lui sont appliquées, il existe un petit délai avant que la sortie correspondante ne soit disponible. Donc,

si l'on utilise plusieurs portes en cascade, il faut ajouter les temps de propagation de toutes les portes.

Pour obtenir une fonction quelconque, on associe des portes simples ou composées entre elles, en essayant de réduire leur nombre au maximum, c'est à dire en simplifiant la fonction au préalable.

#### Portes universelles

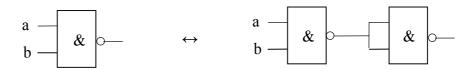

Les portes NON-ET et NON-OU sont appelées portes universelles car elles permettent d'obtenir n'importe laquelle des 3 fonctions logiques de base (NON, OU, ET).

Le NON peut être obtenu par une porte NON-ET dont les entrées sont reliées entre elles :

Le ET peut être obtenu par une porte NON-ET en série avec une autre montée en inverseur (=fonction NON) :

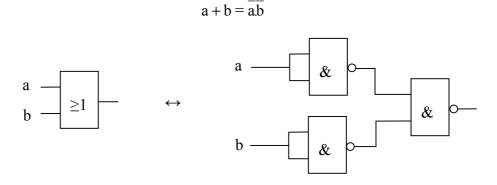

Le OU peut être obtenu par 2 NON-ET montés en inverseurs en entrée d'un 3<sup>e</sup> NON-ET : Cette équivalence correspond à l'égalité :

Pour le NON-OU, il suffit de rajouter un inverseur supplémentaire.

En remplaçant les portes NON-ET par des portes NON-OU, on obtiendrait pour le dernier schéma la fonction ET.

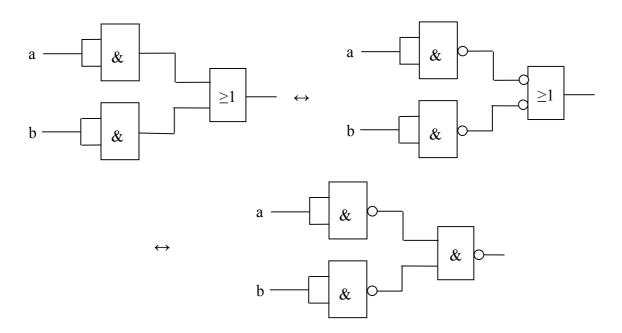

# Transformation d'un circuit en portes NON-ET

Dans l'exemple suivant, on peut inverser les signaux en sortie de portes, mais également en entrée ; cela peut faciliter les conversions.

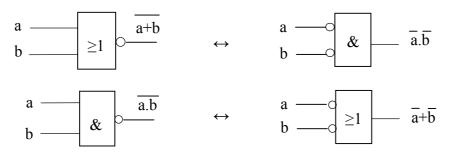

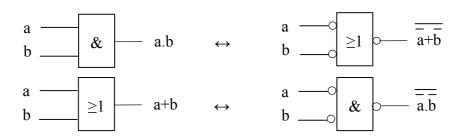

La dernière transformation utilise le théorème de DeMorgan. La propriété duale de DeMorgan correspond aux équivalences :

De même :

# Partie II) Logique combinatoire

Un circuit combinatoire possède un certain nombre d'entrées et un certain nombre de sorties. Les sorties sont reliées aux entrées par des fonctions logiques. L'aspect temporel n'intervient pas, contrairement aux circuits logiques séquentiels.

Ces circuits sont établis à partir d'une opération appelée synthèse combinatoire. La synthèse combinatoire est la traduction d'une fonction logique, à partir d'un cahier des charges, en un schéma. Diverses méthodes de synthèse sont possibles ; elles diffèrent sur la forme de la fonction utilisée (canonique ou simplifiée), sur le type des opérateurs ou des circuits intégrés choisis, et sur la technique de découpage fonctionnel employée.

Dans cette partie, nous allons étudier quelques grandes fonctions combinatoires couramment utilisées.

## II.1) Codeur/décodeur binaire

Ce mot désigne l'ensemble des codeurs, décodeurs et convertisseurs de code. Ces circuits transforment une information codée sous une certaine forme, en une information équivalente mais codée sous une autre forme.

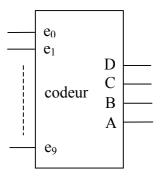

#### II.1.1) Codeur

Un codeur (sous-entendu binaire) est un circuit logique codant en sortie l'indice de son entrée active (= "à 1", en logique positive). Sa condition de fonctionnement est donc qu'il n'y ait qu'une seule entrée active en même temps.

Pour n sorties, il peut posséder 2<sup>n</sup> entrées.

Un exemple d'application de ce type de codeur est la commande d'une opération d'une machine par un groupe de boutons-poussoirs, dont un seul peut être activé en même temps.

La table de vérité de ce codeur est la suivante (elle comporte une colonne supplémentaire indiquant la valeur décimale N correspondant à l'indice de l'entrée active) :

| N | e <sub>9</sub> | e <sub>8</sub> | e <sub>7</sub> | e <sub>6</sub> | e <sub>5</sub> | $e_4$ | $e_3$ | $e_2$ | $e_1$ | $e_0$ | A | В | С | D |

|---|----------------|----------------|----------------|----------------|----------------|-------|-------|-------|-------|-------|---|---|---|---|

| 0 | 0              | 0              | 0              | 0              | 0              | 0     | 0     | 0     | 0     | 1     | 0 | 0 | 0 | 0 |

| 1 | 0              | 0              | 0              | 0              | 0              | 0     | 0     | 0     | 1     | 0     | 0 | 0 | 0 | 1 |

| 2 | 0              | 0              | 0              | 0              | 0              | 0     | 0     | 1     | 0     | 0     | 0 | 0 | 1 | 0 |

| 3 | 0              | 0              | 0              | 0              | 0              | 0     | 1     | 0     | 0     | 0     | 0 | 0 | 1 | 1 |

| 4 | 0              | 0              | 0              | 0              | 0              | 1     | 0     | 0     | 0     | 0     | 0 | 1 | 0 | 0 |

| 5 | 0              | 0              | 0              | 0              | 1              | 0     | 0     | 0     | 0     | 0     | 0 | 1 | 0 | 1 |

| 6 | 0              | 0              | 0              | 1              | 0              | 0     | 0     | 0     | 0     | 0     | 0 | 1 | 1 | 0 |

| 7 | 0              | 0              | 1              | 0              | 0              | 0     | 0     | 0     | 0     | 0     | 0 | 1 | 1 | 1 |

| 8 | 0              | 1              | 0              | 0              | 0              | 0     | 0     | 0     | 0     | 0     | 1 | 0 | 0 | 0 |

| 9 | 1              | 0              | 0              | 0              | 0              | 0     | 0     | 0     | 0     | 0     | 1 | 0 | 0 | 1 |

Par exemple si l'entrée  $e_6$  est active (N=6), le mot de sortie est (D,C,B,A) = (0,1,1,0).

On cherche maintenant à déterminer les fonctions logiques de chacune des sorties, ce qui est nécessaire si l'on veut réaliser ce circuit physiquement.

On pourrait passer par les tableaux de Karnaugh, mais en fait on va voir que cela n'est pas nécessaire. En effet, une seule des entrées étant à 1 en même temps, toutes les combinaisons binaires d'entrée ne sont pas utilisées. Vérifions sur un cas simple à 2 entrées :

| N | $e_3$ | $e_2$ | $e_1$ | $e_0$ | В | A<br>0 |

|---|-------|-------|-------|-------|---|--------|

| 0 | 0     | 0     | 0     | 1     | 0 | 0      |

| 1 | 0     | 0     | 1     | 0     | 0 | 1      |

| 2 | 0     | 1     | 0     |       |   | 0      |

| 3 | 1     | 0     | 0     | 0     | 1 | 1      |

La fonction logique donnant les valeurs de A correctes sont :

$$A = \overline{e_3} \cdot \overline{e_1} \cdot \overline{e_0} + \overline{e_3} \cdot \overline{e_2} \cdot \overline{e_1} \cdot \overline{e_0}$$

En supposant qu'on n'aura jamais le cas où 2 entrées sont à 1 en même temps, on peut simplifier le tableau de Karnaugh correspondant en le complétant par des états indéterminés:

| $\langle e_3 e_2 \rangle$<br>$e_1 e_0 \rangle$ | 00 | 01 | 11 | 10 |

|------------------------------------------------|----|----|----|----|

| 00                                             |    | 0  | X  | 1  |

| 01                                             | 0  |    | X  | X  |

| 11                                             | X  | X  | X  | X  |

| 10                                             | 1  | X  | X  | X  |

ce qui donne pour A:

$$A = e_1 + e_3$$

On voit bien quelle est la simplification apportée par le tableau de Karnaugh : la sortie A est la somme des 2 entrées actives pour lesquelles elle vaut 1.

On peut donc déterminer directement la fonction à partir de la table de vérité, et ceci quel que soit le nombre d'entrées.

Ainsi, dans le cas de 10 entrées, on peut déterminer directement :

$$A = e_1 + e_3 + e_5 + e_7 + e_9$$

$$B = e_2 + e_3 + e_6 + e_7$$

$$C = e_4 + e_5 + e_6 + e_7$$

$$D = e_8 + e_9$$

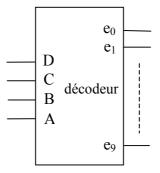

#### II.1.2) Décodeur

Le décodeur binaire réalise la fonction inverse de celle du codeur. Il possède n entrées et 2<sup>n</sup> sorties. On peut considérer que ce circuit code en décimal (chacune des sorties étant associée à un chiffre décimal différent) l'entrée codée en binaire.

Par exemple, quand on a (D,C,B,A) = (0,0,1,1), la sortie d'indice 3  $(e_3)$  est à 1.

# Structure logique interne

Elle se déduit de la table de vérité :

| A | В | С | D | N | S9 | S <sub>8</sub> | S <sub>7</sub> | S <sub>6</sub> | <b>S</b> 5 | S <sub>4</sub> | S <sub>3</sub> | S <sub>2</sub> | $s_1$ | $s_0$ |

|---|---|---|---|---|----|----------------|----------------|----------------|------------|----------------|----------------|----------------|-------|-------|

| 0 | 0 | 0 | 0 | 0 | 0  | 0              | 0              | 0              | 0          | 0              | 0              | 0              | 0     | 1     |

| 0 | 0 | 0 | 1 | 1 | 0  | 0              | 0              | 0              | 0          | 0              | 0              | 0              | 1     | 0     |

| 0 | 0 | 1 | 0 | 2 | 0  | 0              | 0              | 0              | 0          | 0              | 0              | 1              | 0     | 0     |

| 0 | 0 | 1 | 1 | 3 | 0  | 0              | 0              | 0              | 0          | 0              | 1              | 0              | 0     | 0     |

| 0 | 1 | 0 | 0 | 4 | 0  | 0              | 0              | 0              | 0          | 1              | 0              | 0              | 0     | 0     |

| 0 | 1 | 0 | 1 | 5 | 0  | 0              | 0              | 0              | 1          | 0              | 0              | 0              | 0     | 0     |

| 0 | 1 | 1 | 0 | 6 | 0  | 0              | 0              | 1              | 0          | 0              | 0              | 0              | 0     | 0     |

| 0 | 1 | 1 | 1 | 7 | 0  | 0              | 1              | 0              | 0          | 0              | 0              | 0              | 0     | 0     |

| 1 | 0 | 0 | 0 | 8 | 0  | 1              | 0              | 0              | 0          | 0              | 0              | 0              | 0     | 0     |

| 1 | 0 | 0 | 1 | 9 | 1  | 0              | 0              | 0              | 0          | 0              | 0              | 0              | 0     | 0     |

N est la valeur décimale correspondante à l'indice de la sortie active.

On obtient les fonctions suivantes  $s_0, ... s_9$  directement sous forme somme-de-produits :

$$s_0 = \overline{ABCD}$$

,  $s_1 = \overline{ABCD}$ ,  $s_2 = \overline{ABCD}$ , etc

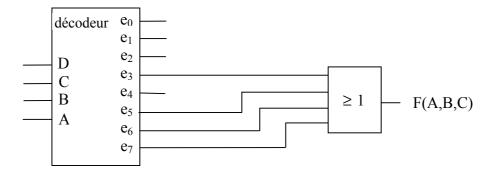

Réalisation d'une fonction logique quelconque au moyen d'un décodeur

Les décodeurs permettent de réaliser n'importe quelle fonction logique. Précédemment, on avait défini les fonctions logiques directement à partir des variables d'entrée. Le résultat correspondait à une réalisation de la fonction en portes logiques élémentaires. L'utilisation d'un décodeur constitue donc une autre manière de réaliser une fonction.

Le problème est similaire à la détermination de la fonction logique d'un codeur vue dans le paragraphe précédent. On définit d'abord la fonction à réaliser en fonction des sorties  $s_i$  du décodeur, de la même manière qu'on avait déterminé les sorties du codeur.

#### Exemple

On cherche à réaliser la fonction  $f(A, B, C) = \Sigma(3, 5, 6, 7)$  avec un décodeur et une porte logique. On remplit la table de vérité de manière adéquate :

| A | В | С | N | <b>S</b> 7 | S <sub>6</sub> | <b>S</b> 5 | S <sub>4</sub> | <b>S</b> 3 | S <sub>2</sub> | $s_1$ | $s_0$ | F(A,B,C) |

|---|---|---|---|------------|----------------|------------|----------------|------------|----------------|-------|-------|----------|

| 0 | 0 | 0 | 0 | 0          | 0              | 0          | 0              | 0          | 0              | 0     | 1     | 0        |

| 0 | 0 | 1 | 1 | 0          | 0              | 0          | 0              | 0          | 0              | 1     | 0     | 0        |

| 0 | 1 | 0 | 2 | 0          | 0              | 0          | 0              | 0          | 1              | 0     | 0     | 0        |

| 0 | 1 | 1 | 3 | 0          | 0              | 0          | 0              | 1          | 0              | 0     | 0     | 1        |

| 1 | 0 | 0 | 4 | 0          | 0              | 0          | 1              | 0          | 0              | 0     | 0     | 0        |

| 1 | 0 | 1 | 5 | 0          | 0              | 1          | 0              | 0          | 0              | 0     | 0     | 1        |

| 1 | 1 | 0 | 6 | 0          | 1              | 0          | 0              | 0          | 0              | 0     | 0     | 1        |

| 1 | 1 | 1 | 7 | 1          | 0              | 0          | 0              | 0          | 0              | 0     | 0     | 1        |

On en déduit alors l'expression de f, de la même manière qu'on l'avait fait pour le codeur :

$$F(A,B,C) = s_3 + s_5 + s_6 + s_7$$

On peut alors en déduire le schéma correspondant :

#### II.2) Transcodeurs

Un transcodeur est un convertisseur de code. Il existe un grand nombre de transcodeurs possibles. Ce paragraphe décrit un type de transcodeur couramment utilisé : le transcodeur 7 segments.

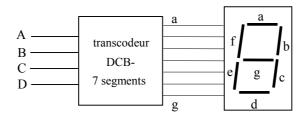

#### II.2.1) Transcodeur DCB-7 segments

Un transcodeur DCB-7 segments permet de générer les signaux logiques adéquats pour afficher sur un afficheur à 7 segments la valeur décimale (de 0 à 9) correspondant à la valeur binaire de l'entrée.

Un afficheur à 7 segments est composé de 7 LEDs (pour Light Emitting Diode, ou DEL pour Diode Emettrice de Lumière, en français), pouvant être commandées par des niveaux logiques. Selon le type de LED utilisé, un niveau 1 peut se traduire par l'allumage ou son extinction, et inversement pour le niveau 0.

Dans les applications pratiques (par exemple, affichage de la somme d'argent entrée dans un distributeur de boissons), on veut afficher les valeurs décimales (de 0 à 9) et non pas les valeurs hexadécimales (de 0 à 9, puis A à F). C'est pourquoi on parle de Décimal Codé en Binaire (BCD en anglais). Cela signifie que l'on n'utilise que les 10 premières valeurs du code hexadécimal qui en comporte 16 (codés sur 4 bits).

Sur le schéma ci-dessous, les 4 entrées sont appelées A, B, C, D et les 7 sorties a, b, c, d, e, f, g.

Chacune des 7 sorties de ce transcodeur correspond à une fonction logique différente. La table de vérité correspondante comporte donc 4 entrées et 7 sorties.

Supposons que les afficheurs utilisés nécessitent un 1 logique pour l'allumage de ses segments. Pour chaque ligne de la table de vérité, on place des 1 dans une colonne lorsque l'on souhaite que le segment correspondant soit allumé pour l'entrée codée dans cette ligne.

Par exemple, pour la combinaison

$$(A, B, C, D) = (0, 0, 1, 0)$$

on souhaite que le chiffre 2 s'affiche. Pour cette ligne, les colonnes correspondant aux segments a, b, d, e, g doivent donc comporter un 1.

Une fois la table de vérité déterminée, il reste à simplifier les fonctions des 7 segments. On peut utiliser pour cela des tableaux de Karnaugh.

Il est important de remarquer toutes les combinaisons possibles ne sont pas utilisées. Comme indiqué plus haut, les "trous" correspondant dans les tableaux de Karnaugh correspondent aux combinaisons d'entrée non-utilisées. Si l'on est sûr que ces combinaisons n'apparaîtront jamais sur les entrées, on peut considérer les états correspondants des sorties comme indéterminés. On les remplace par des 0 ou des 1 selon les cas, pour simplifier au maximum les fonctions. Par contre, si ces combinaisons peuvent se produire et qu'on souhaite qu'elles ne provoquent pas d'allumage des LEDs, il faut mettre les sorties correspondantes à 0.

#### II.2.2) Autres transcodeurs

Le transcodage est un principe général dans lequel le nombre de bits du code d'entrée et celui du code de sortie peuvent être quelconques. On peut par exemple vouloir réaliser un transcodage du code binaire naturel vers le code de Gray, ou bien l'inverse.

Le transcodeur DCB-7 segments étudié au paragraphe précédent n'est qu'un exemple d'application pratique de ce principe. Le codeur et le décodeur sont deux cas particuliers de transcodeurs.

Quel que soit le transcodeur recherché, la méthode de synthèse est exactement la même que celle utilisée pour le transcodeur DCB-7 segments. De plus, comme pour ce dernier, il peut y avoir des combinaisons d'entrées non-utilisées, auxquelles correspondent des états indéterminés des sorties. Ces derniers peuvent être mis à profit pour simplifier les équations logiques des sorties.

# II.3) Multiplexeur/démultiplexeur

Les multiplexeurs et démultiplexeurs sont des circuits combinatoires couramment utilisés. Les premiers permettent, entre autre, de transformer des données parallèles en

données série, d'utiliser un même circuit intégré pour plusieurs signaux (et donc de simplifier les circuits), mais également de synthétiser n'importe quelle fonction logique. Les seconds permettent, entre autres, de réaliser la conversion série-parallèle.

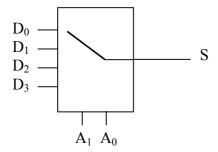

#### II.3.1) Multiplexeur

Principe

C'est un circuit qui possède

- des entrées de commande (ou d'adresse), au nombre de  $n:A_{n\text{-}1}\ldots A_0$ ;

- des entrées de données, au nombre de  $2^n$  :  $D_2^{n}$ -1... $D_0$  ;

- une sortie S.

Un multiplexeur est qualifié par rapport à ses entrées de données. Par exemple, on parle de multiplexeur 8 vers 1 pour 8 entrées de donnée et 3 entrées d'adresse. Le multiplexeur peut être vu comme un commutateur commandé par les entrées d'adresse : selon la valeur des entrées d'adresse, une des entrées de données sera connectée en sortie.

Supposons un multiplexeur à deux entrées adresses  $A_1$  et  $A_0$ ; pour chaque combinaison binaire de  $(A_1, A_0)$ , une entrée de donnée sera connectée en sortie. Par exemple, pour  $(A_1, A_0)=10$ , l'entrée  $D_2$  sera connectée en sortie.

La table de vérité correspondante est la suivante :

| ٨     | ٨     | Entrée         |

|-------|-------|----------------|

| $A_1$ | $A_0$ | sélectionnée   |

| 0     | 0     | $\mathrm{D}_0$ |

| 0     | 1     | $D_1$          |

| 1     | 0     | $D_2$          |

| 1     | 1     | $D_3$          |

On en déduit la fonction logique de sortie. Chaque ligne de la table correspond à un terme d'une somme de produits. On détermine chacun de ces termes de la même façon que pour une fonction logique composée de 0 et de 1, sauf que chaque combinaison d'entrée est multipliée par la valeur correspondante de la fonction :

$$S = D_0 \overline{A_0 A_1} + D_1 A_0 \overline{A_1} + D_2 \overline{A_0 A_1} + D_3 A_0 A_1$$

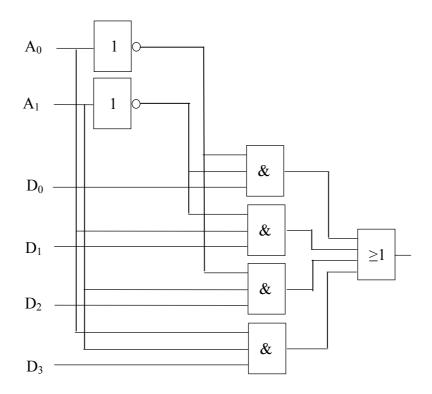

#### Réalisation

Le schéma se déduit directement de l'expression de la sortie :

Exemple d'application d'un multiplexeur : réalisation d'une fonction quelconque

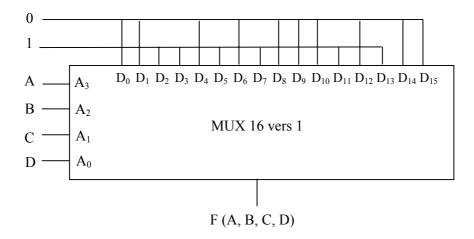

Soit la fonction  $F(A, B, C, D) = \sum (2, 3, 5, 7, 11, 13)$ .

On cherche à réaliser cette fonction avec une multiplexeur à quatre entrées d'adresses,  $A_0$  à  $A_3$ , et  $2^4$ =16 entrées de données,  $D_0$  à  $D_{15}$ .

En utilisant les variables A, B, C, D de F comme entrées d'adresse du multiplexeur, il suffit de relier l'entrée sélectionnée par chaque adresse à 0 ou à 1, selon que F vaut 0 ou 1 pour la combinaison correspondante des variables. On obtient donc le schéma suivant :

On peut également réaliser cette même fonction avec un multiplexeur possédant moins d'entrées d'adresse que de variables. Il faut alors exprimer la fonction en fonction des variables non-utilisées comme entrées d'adresse.

Pour cela on peut s'aider de la table de vérité de F:

| A | В | С | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |

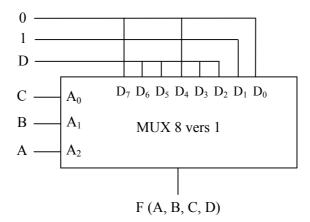

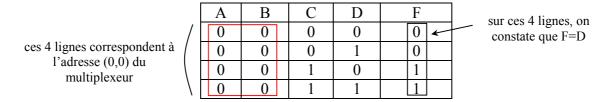

Par exemple, avec 3 entrées d'adresse seulement, une solution consiste à utiliser 3 des variables comme entrées d'adresse (par exemple A, B et C), et d'exprimer F en fonction de la variable non utilisée (ici, D).

Chacune des combinaisons des entrées d'adresse occupe 2 lignes. Sur ces 2 lignes, il faut exprimer F en fonction de D. On aura 4 cas possibles : F=0, F=1, F=D ou  $F=\overline{D}$ .

Par exemple, la première adresse : (A, B, C)=(0, 0, 0) correspond aux 2 première lignes de la table de vérité. Il faut trouver l'expression de F sur ces 2 lignes. On constate que l'on a F=0. Il faut donc relier l'entrée  $D_0$  du multiplexeur (celle qui est sélectionnée par l'adresse (0,0,0)) à 0 :

|                                   | A | В | C | D | F | sur ces 2 lignes, F=0 |

|-----------------------------------|---|---|---|---|---|-----------------------|

| ces 2 lignes correspondent à      | 0 | 0 | 0 | 0 | 0 | sur ccs 2 fighes, 1-0 |

| l'adresse (0,0,0) du multiplexeur | 0 | 0 | 0 | 1 | 0 |                       |

| mantpiexeur                       | 0 | 0 | 1 | 0 | 1 |                       |

|                                   | 0 | 0 | 1 | 1 | 1 |                       |

On applique le même principe pour toutes les autres combinaisons de (A,B,C). On obtient le schéma suivant :

*Remarque* : on aurait pu utiliser n'importe laquelle des 4 variables pour les 3 entrées d'adresse du multiplexeur. La lecture de l'expression de F à partir de la table de vérité aurait simplement été un peu moins directe (il aurait fallu regarder la valeur de F sur 2 lignes non-adjacentes).

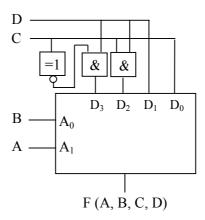

Avec une multiplexeur à deux entrées d'adresse seulement., le principe à appliquer est le même que précédemment : il faut exprimer F pour chacune des adresses, en fonction des variables non-utilisées comme entrées d'adresse.

On choisit d'utiliser les variables A et B comme entrées d'adresse. Par exemple, pour la première adresse (0,0), on détermine l'expression de F en fonction de C et D (les 2 variables non-utilisées comme entrées d'adresse), sur les 4 premières lignes de la table de vérité :

et ainsi de suite. On obtient alors le schéma complet suivant :

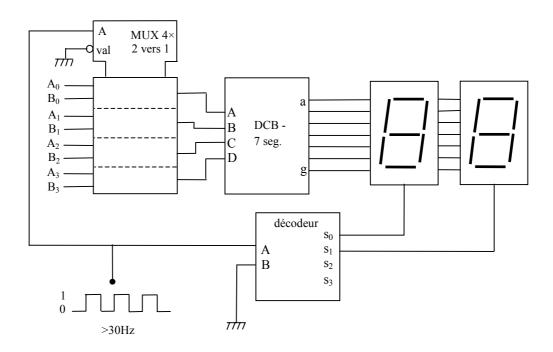

Autre exemple d'application : commande de plusieurs afficheurs 7 segments

Un multiplexeur permet également d'utiliser un même circuit intégré pour traiter plusieurs données. Par exemple, on peut utiliser un seul transcodeur BCD-7 segments pour commander plusieurs afficheurs à 7 segments.

Par exemple, on souhaite afficher 2 chiffres décimaux sur 2 afficheurs à 7 segments. Ces 2 chiffres sont codés en binaire, sur 2 mots de 4 bits : A<sub>3</sub>, A<sub>2</sub>, A<sub>1</sub>, A<sub>0</sub> et B<sub>3</sub>, B<sub>2</sub>, B<sub>1</sub>, B<sub>0</sub>. L'idée est d'utiliser un multiplexeur pour présenter alternativement ces 2 mots binaires en entrée du transcodeur BCD-7 segments. Si, dans le même temps et de manière synchrone, on active alternativement les 2 afficheurs 7 segments, et si la fréquence de cette commutation est supérieure à 20-30Hz, l'utilisateur verra chacun des 2 chiffres sur un afficheur dédié. Le multiplexeur à utiliser ici est un quadruple 2-vers-1. L'activation d'un seul des 2 afficheurs peut être obtenue au moyen d'un codeur, commandé par le même signal que celui commandant le multiplexeur (sur son unique entrée d'adresse A).

Un schéma implantant cette idée pourrait être le suivant :

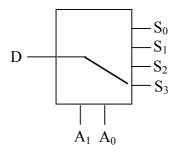

#### II.3.2) Démultiplexeurs

Un démultiplexeur réalise l'opération inverse de celle du multiplexeur. Il s'agit d'un circuit possédant :

- n entrées de commande (ou d'adresse) :  $A_{n-1}...A_0$ ;

- $-2^{n}$  sorties :  $S_{2}^{n}$  -1... $S_{0}$ ;

- une entrée de donnée D.

Un démultiplexeur recopie l'entrée D sur la sortie correspondant à la valeur présente sur les entrées d'adresse. Une sortie non sélectionnée est à 0.

Pour un démultiplexeur à 2 entrées d'adresse, si on a par exemple  $(A_1, A_0)=11$ , la sortie 3 est connecté à D :

La table de vérité correspondante est la suivante :

| $A_1$ | $A_0$ | $S_3$ | $S_2$ | $S_1$ | $S_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | D     |

| 0     | 1     | 0     | 0     | D     | 0     |

| 1     | 0     | 0     | D     | 0     | 0     |

| 1     | 1     | D     | 0     | 0     | 0     |

Les expressions logiques des sorties s'en déduisent :

$$S_0 = D\overline{A_1}\overline{A_0}$$

,  $S_1 = D\overline{A_1}A_0$ ,  $S_2 = D.A_1\overline{A_0}$ ,  $S_3 = D.A_1.A_0$

On peut remarquer que lorsque l'entrée vaut toujours 1, un démultiplexeur devient un décodeur (et donc qu'un décodeur est un cas particulier du multiplexeur).

## II.4) Comparateur

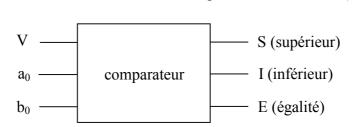

Un comparateur permet de comparer 2 mots binaires, c'est à dire d'indiquer si ces 2 mots sont égaux, mais également, si ça n'est pas le cas, lequel est le plus grand. Il est basé sur l'utilisation d'un comparateur 1 bit.

#### II.4.1) Comparateur d'égalité

Deux mots binaires sont égaux si leurs éléments binaires de même poids sont égaux deux à deux. Par exemple, 2 mots de 4 bits A  $(A_3, A_2, A_1, A_0)$  et B  $(B_3, B_2, B_1, B_0)$  sont égaux si  $A_3 = B_3$  et  $A_2 = B_2$  et  $A_1 = B_1$  et  $A_0 = B_0$ .

On a vu plus haut que la fonction NON OU-EXCLUSIF à 2 entrées était un détecteur d'égalité entre ces 2 bits, c'est à dire que la fonction valait 1 si ces 2 bits étaient égaux, 0 s'ils étaient différents.

Pour comparer plusieurs bits, il suffit donc d'associer plusieurs fonctions NON OU-EXCLUSIF en série. La fonction permettant de détecter l'égalité des 2 mots binaires de l'exemple est donc :

$$f(A = B) = (\overline{A_3 \oplus B_3})(\overline{A_2 \oplus B_2})(\overline{A_1 \oplus B_1})(\overline{A_0 \oplus B_0})$$

## II.4.2) Comparateur complet

On souhaite réaliser un comparateur complet de deux mots de 4 bits. Un comparateur complet de 1 bit possède non seulement une sortie signalant l'identité de ses 2 bits d'entrée, mais également une sortie signalant que la 1<sup>ère</sup> est supérieure à la 2<sup>e</sup>, et une sortie signalant l'inverse. Soient a<sub>0</sub> et b<sub>0</sub> ces 2 entrées. Appelons E, S et I respectivement ces 3 sorties :

- E=1 si  $a_0=b_0$ ,

- S=1 si  $a_0 > b_0$ ,

- $I=1 \text{ si } a_0 < b_0$ .

La table de vérité de ce comparateur est la suivante :

| $a_0$ | $b_0$ | S | I | Е |

|-------|-------|---|---|---|

| 0     | 0     | 0 | 0 | 1 |

| 0     | 1     | 0 | 1 | 0 |

| 1     | 0     | 1 | 0 | 0 |

| 1     | 1     | 0 | 0 | 1 |

On en déduit les équations des sorties :

$$S = a_0 \overline{b_0}$$

,  $I = \overline{a_0} b_0$ ,  $E = \overline{a_0 \oplus b_0}$

Le comparateur peut être schématisé par le bloc fonctionnel suivant. L'entrée V est une entrée de validation. Le comparateur fonctionne si V est égal à 1, sinon toutes les sorties sont égales à 0 (on en verra l'utilité dans l'association de plusieurs de ces blocs).

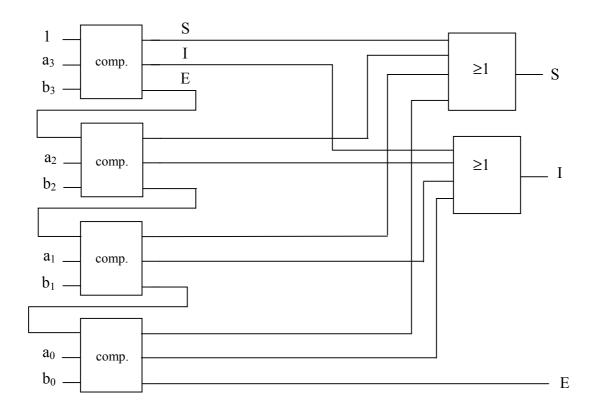

Nous cherchons maintenant à réaliser un comparateur de deux mots de quatre bits  $A(a_0, a_1, a_2, a_3)$  et  $B(b_0, b_1, b_2, b_3)$  à l'aide de comparateurs 1-bit mis en cascade et de quelques portes logiques.

Le comparateur doit indiquer s'il y a égalité de ses 2 mots binaires d'entrée, et sinon lequel est le plus grand, par l'intermédiaire de ses 3 sorties E, S et I.

L'idée est de comparer les bits correspondants 1 à 1 en partant de celui de poids le plus fort.

Si le bit de poids le plus fort du 1<sup>er</sup> mot est 1 et celui du 2<sup>e</sup> sont les mêmes, on n'est pas renseigné sur la comparaison de ces 2 mots donc il faut aller voir le bit de poids immédiatement inférieur. Et ainsi de suite jusqu'aux bits de poids le plus faible.

Si l'un des bits est 0 et le bit correspondant de l'autre mot est 1, il n'est pas nécessaire d'aller tester les bits de poids plus faibles, on connaît le résultat. Il faut alors utiliser les informations de S et de I au moyen d'une porte OU. Pour réaliser ceci, on peut relier la sortie locale  $E_i$  d'un comparateur 1-bit à l'entrée de validation du suivant ; ainsi, dès qu'un bit sera différent du bit correspondant de l'autre mot, E sera égale à 0 et inhibera la comparaison des bits de poids inférieurs.

Si les 2 mots sont égaux, la sortie E du comparateur des bits de poids les plus faibles sera à 1. Elle peut donc constituer la sortie d'égalité des 2 mots complets.

La sortie S (supérieur) doit être à 1 si l'une des sorties  $S_i$  est à 1. Elles doivent donc être combinées par une porte OU (à 4 entrées ici). C'est le même principe pour la sortie I.

On obtient donc le schéma suivant pour ce comparateur :

Un des inconvénients de cette structure est que le résultat de la comparaison apparaît après un temps lié aux nombres de portes logiques traversées. Pour palier à cet inconvénient, il faudrait utiliser une structure parallèle (non étudiée ici).

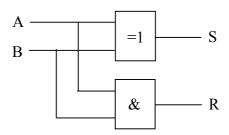

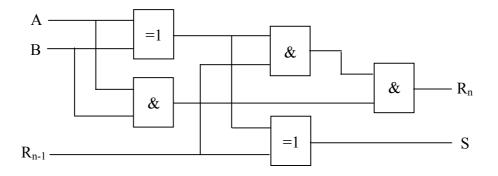

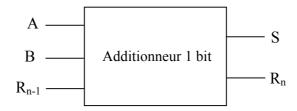

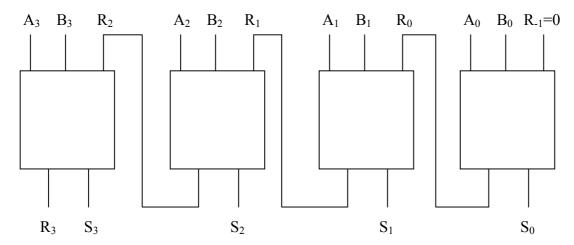

## II.5) Les Additionneurs

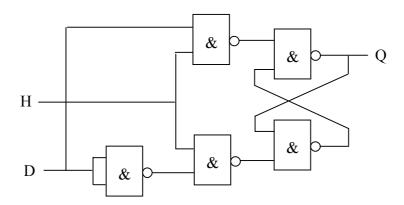

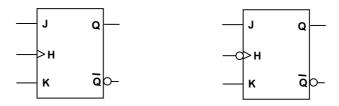

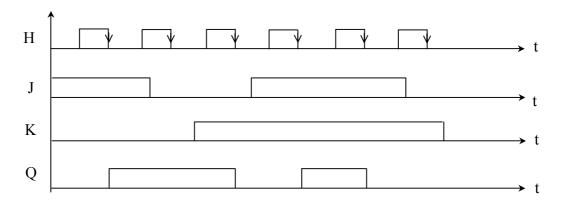

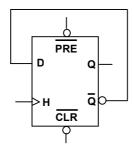

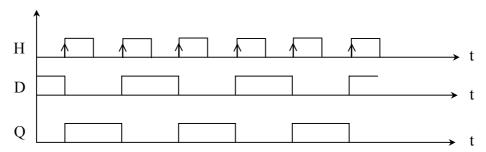

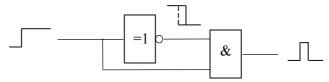

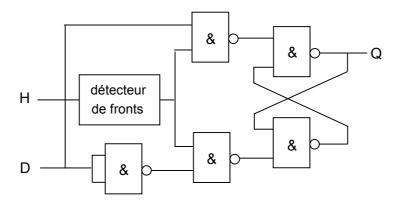

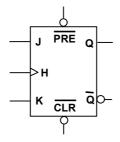

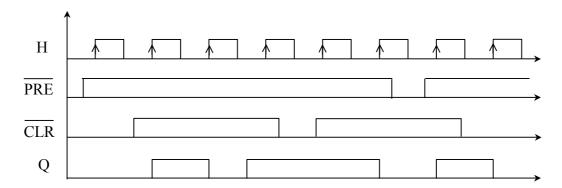

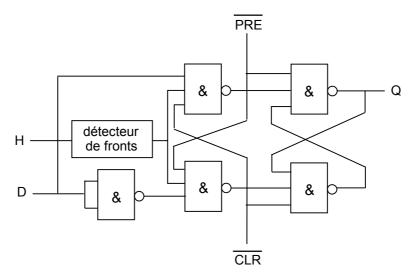

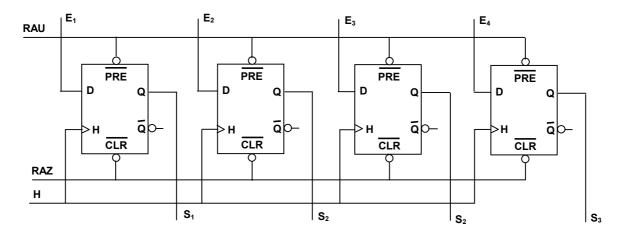

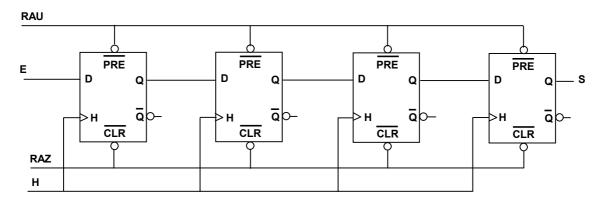

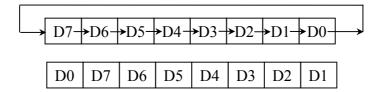

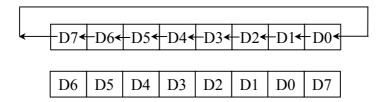

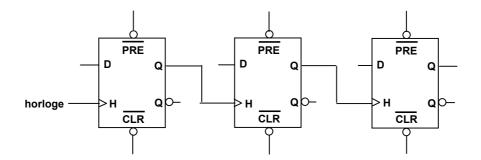

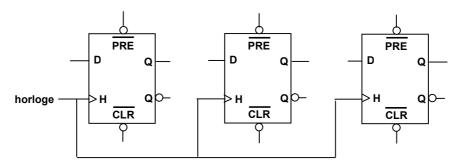

Il s'agit ici de l'addition arithmétique. Le symbole utilisé est le +, mais l'opération est différente de la somme logique.